This article is more than 1 year old

Team MIPS tries to spoil ARM's party with new 64-bit Warrior, 32-bit microcontroller brains

What a coincidence

Imagination Technologies has decided today – right in the middle of its arch rival ARM's annual technical conference in California – is the best day to announce some new chip designs.

As a friendly reminder that ARM doesn't have the world of embedded processors completely sewn up, Imagination will unveil the 64-bit MIPS P6600 CPU – the latest addition to its P-class Warrior family – plus the M6200 and M6250, which are two 32-bit microcontroller-class blueprints.

This week is ARM TechCon week in Santa Clara, a conference aimed at software and hardware engineers wrangling together the insides of smartphones, tablets, embedded systems, and gadgets. The ARM architecture dominates the mobile world, although has competition in the embedded space from MIPS. It's a clash of the Brits: ARM is headquartered in Cambridge, England, while ImgTec hails from Kings Langley in Hertfordshire.

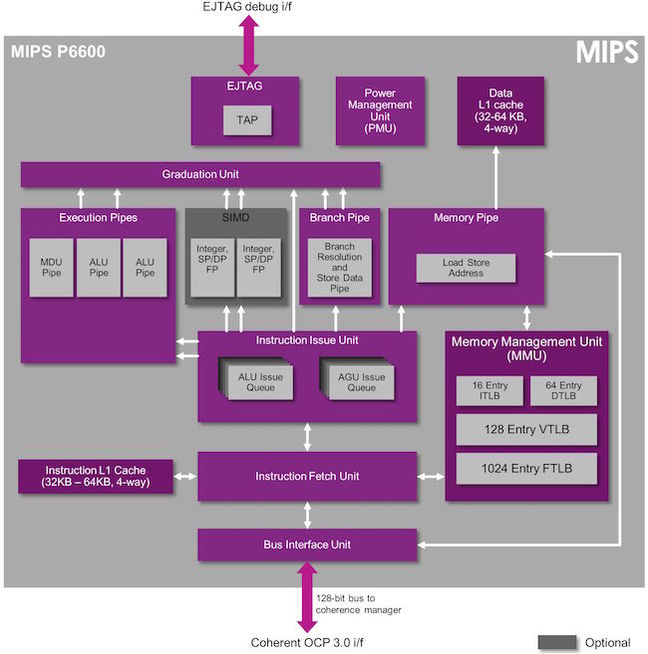

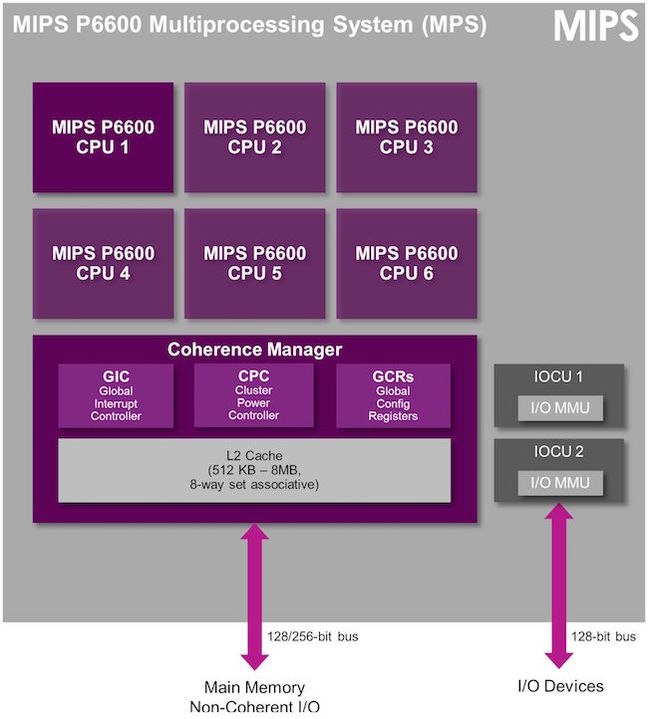

The P6600 succeeds the P5600 Warrior launched in 2013: it has a 16-stage pipeline with multi-issue out-of-order execution, can scale from single core to hexacore, features OmniShield hardware virtualization, and is the first MIPS64 member of the P-class Warrior clan. The P stands for performance: it's aimed primarily at routers and networking gear, and high-end smart TVs and set-top boxes. As a general-purpose processor it can be thrown at anything that needs muscle and where beefy x86 or low-power ARM isn't a great fit.

Components ... The block diagram of a P6600 core

A family now ... How the P6600 cores are grouped to form a single processor

Meanwhile, way down the scale is the microAptiv-series M6200 and M6250: the former is aimed at real-time embedded systems, and the latter at embedded gear running Linux.

You can find more info on these cores here. ®